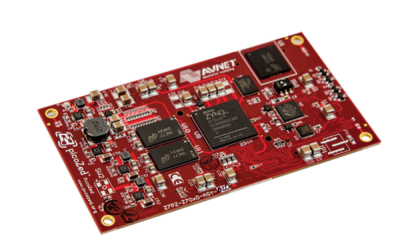

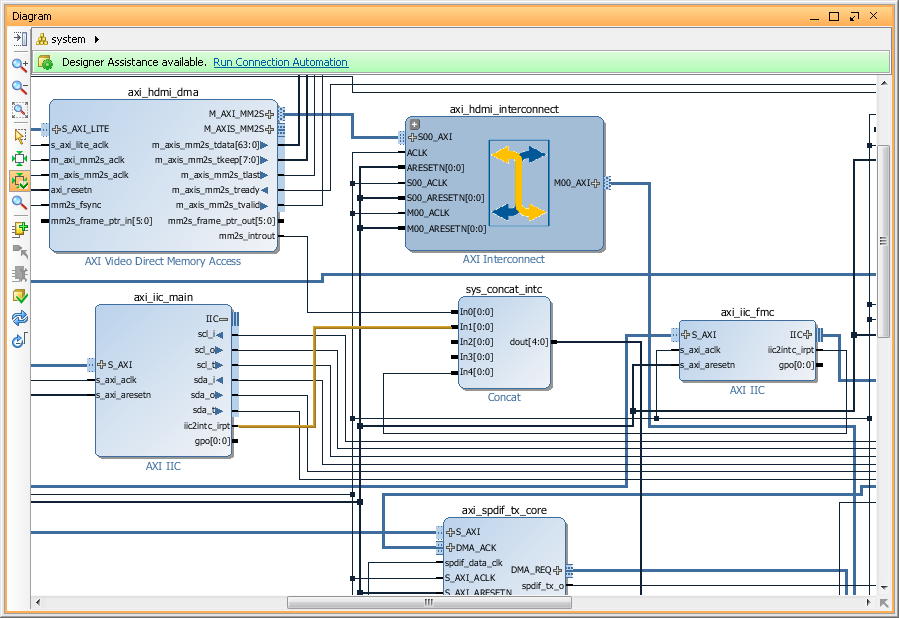

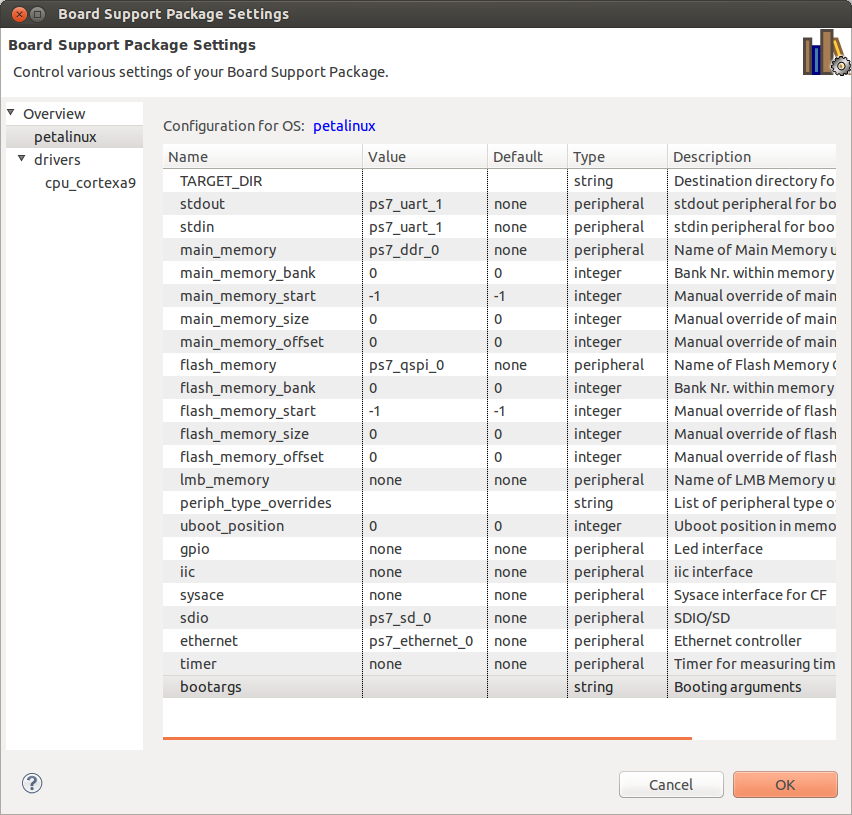

Spent couple of my evenings watching this tutorials and found them painfully slow, but very very useful. Unfortunately for me, I'm already passed that point on my "learning curve" of Zynq and AXI4 bus, but still learned quite a few new tricks and got some ideas, especially on creation of AXI peripheral using HLS and RTL design flows. Hope, Mohammadsadegh Sadri will soon move from trivial examples to advanced topics as he promised in his videos.

Anyway, I suggest this tutorials for everyone. Very nice work Mohammadsadegh Sadri !

You can find full list of tutorials here: http://www.googoolia.com/wp/category/zynq-training/