A small, step-by-step tutorial on how to create and package IP. Just as an example, I will create 3-to-8 decoder IP in Xilinx Vivado 2014.1 and connect it to Zynq SPI chip select pins. This is not a Verilog tutorial, so I will give a minimum information required to create Verilog sources.

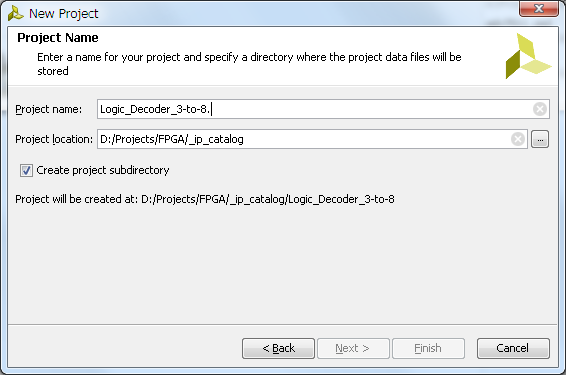

- Run Xilinx Vivado and create new RTL project - name it Logic_Decoder_3-to-8; Specify Verilog as target language; also specify Zynq-7000 for a part family.

- Next step to create IP source file. To do it click on 'Add Sources' in 'Project Manager' group in the Vivado project 'Flow Navigator'.

- In a 'Add Sources' dialog select 'Add or Create Design Sources'.

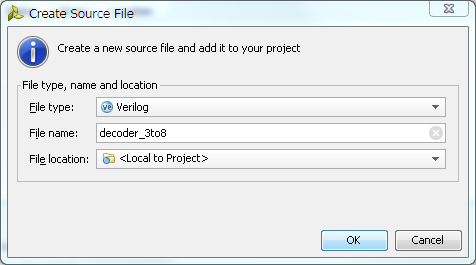

- Then 'Create File...', specify new 'File Name' and click 'Ok' and 'Finish' buttons to close dialogs.

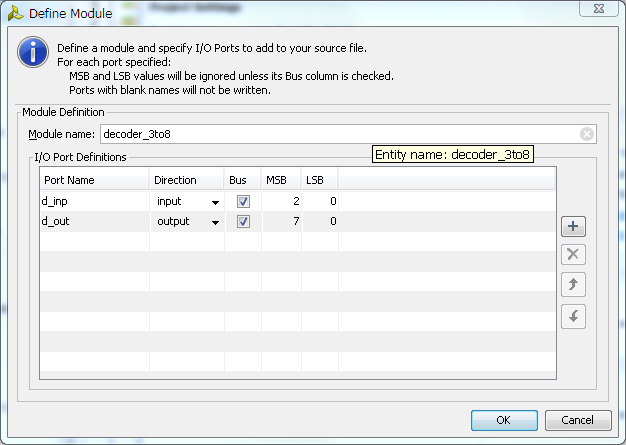

- Next, Vivado will open 'Define Module' dialog where we have to specify inputs and outputs. Since we are creating 3 to 8 decoder, set type of input and output as 'Bus' and set appropriate bus width. Set port names to whatever makes more sense to you, but remember that 'in' and 'out' are reserved words, so you have to be a little creative here. Click 'Ok' close dialog.

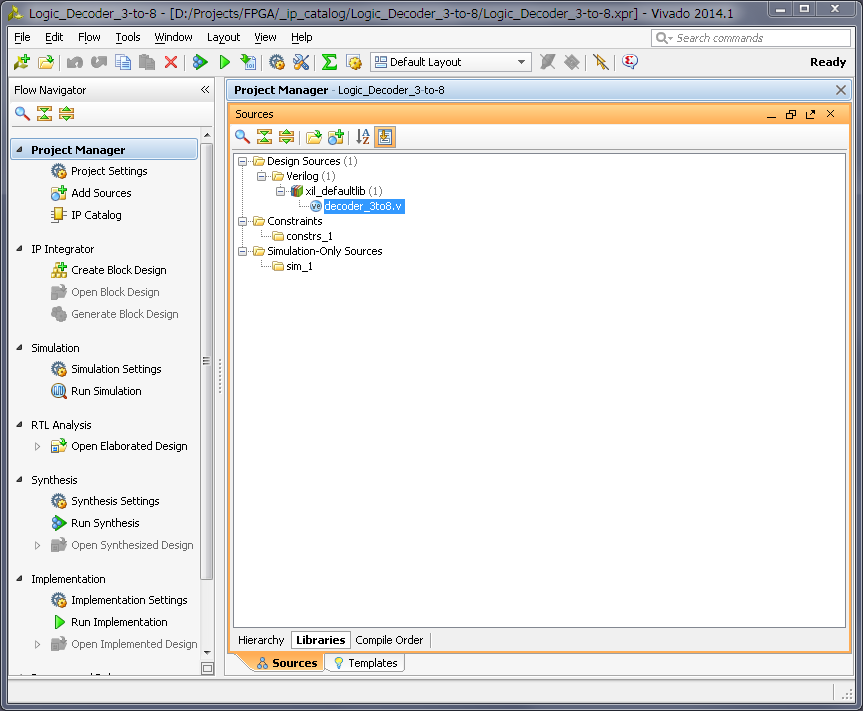

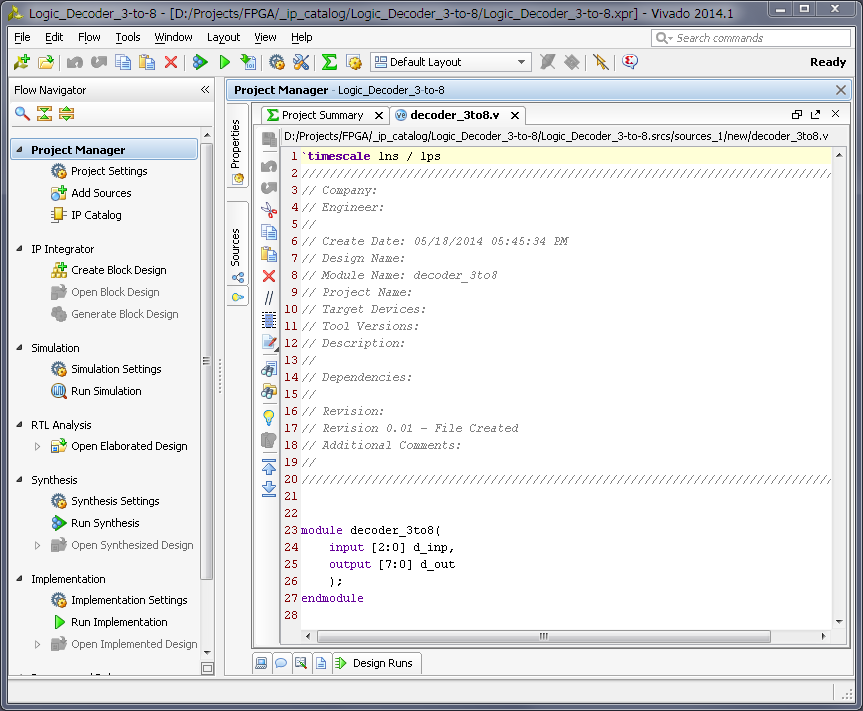

- Now, in a sources window of the Vivado, you can see Verilog source file we just created. Open it.

- This is just a empty source file created using template, but it already have our module input and output defined and all we need to do is to modify it to do an actual address decoding. Below is the one possible solution to such problem.

- Make changes to the source and save it. Now you can run simulation and synthesis and analize the resulted design, but I will skip it to make this tutorial simpler. I also using this very simple verilog module and know it works, but still did verification on it so can just copy-paste it.

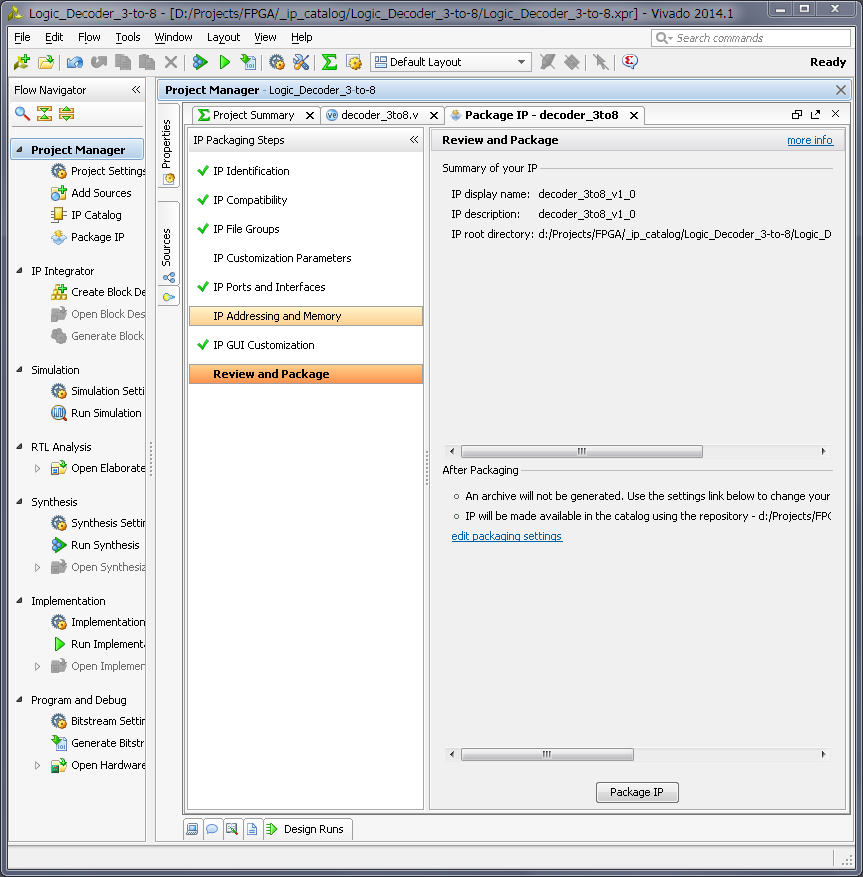

- Now, let's package it. In a 'Tools' menu of the Vivado select 'Create and Package IP...'. Later select 'Package your current project' option, include '.xci' files and 'Finish' new IP creation.

- Change IP identification information if you wish, as well as, any other property for new IP.

- After you done with changes, click on 'Review and Package' menu on the bottom of the list and then click in 'Package IP' button.

- We are done with this IP, close this project.

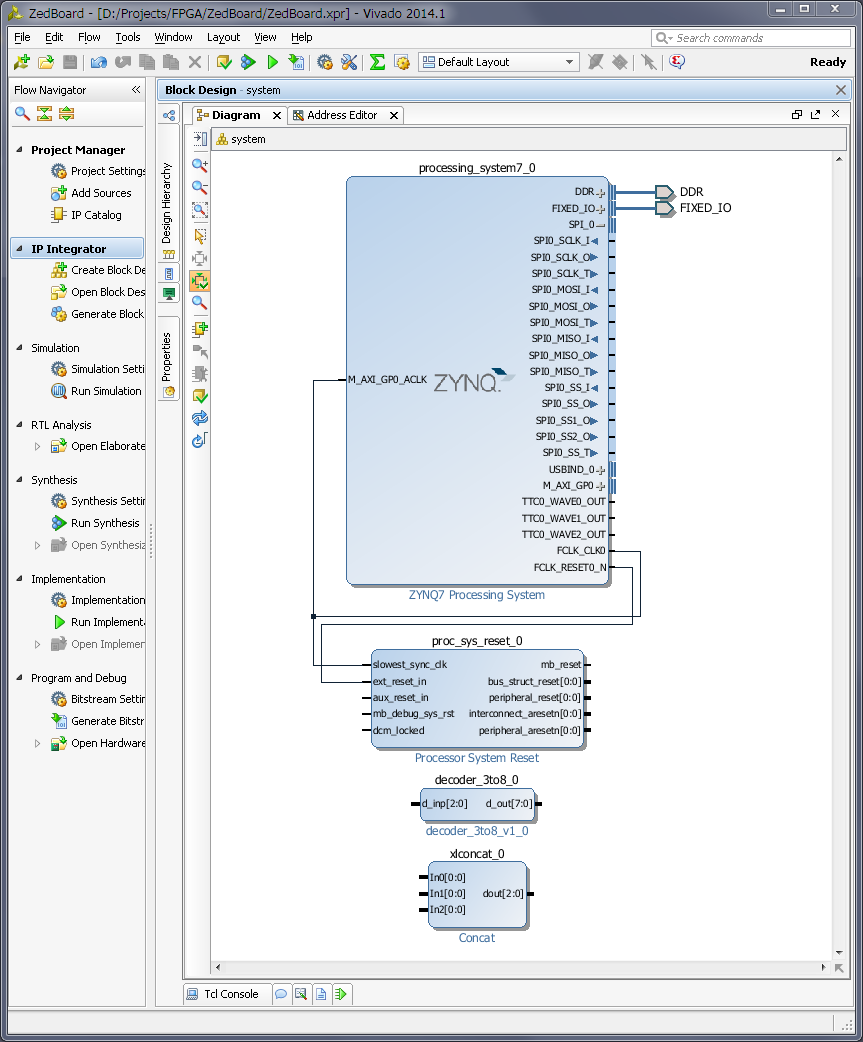

- Now lets use our new 3-to-8 decoder IP. Just for example, I will create new, very basic Zynq design for ZedBoard and will decode one of it's SPI port outputs to 8. And will make them external on one of the ZedBoard PMOD connector. I will not cover creation of the Zynq block design, since I did it in my previous posts.

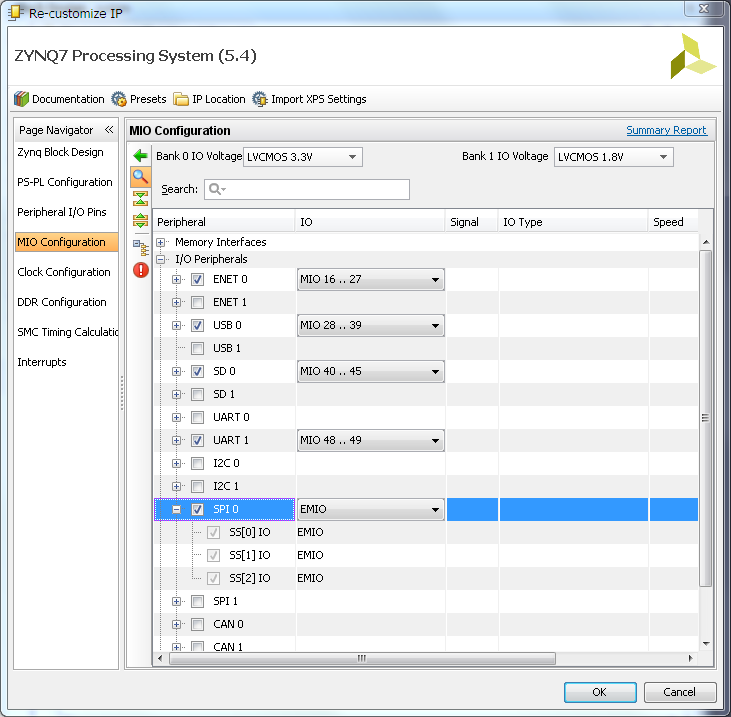

- So, below my simple Zynq block design. Now, I have to enable SPI port. Double click on 'Zynq processing system', go to 'MIO Configuration' and enable 'SPI0' port. As you can see it can only have maximum 3 Slave Select (or Chip Select) pin and sometimes its not enough.

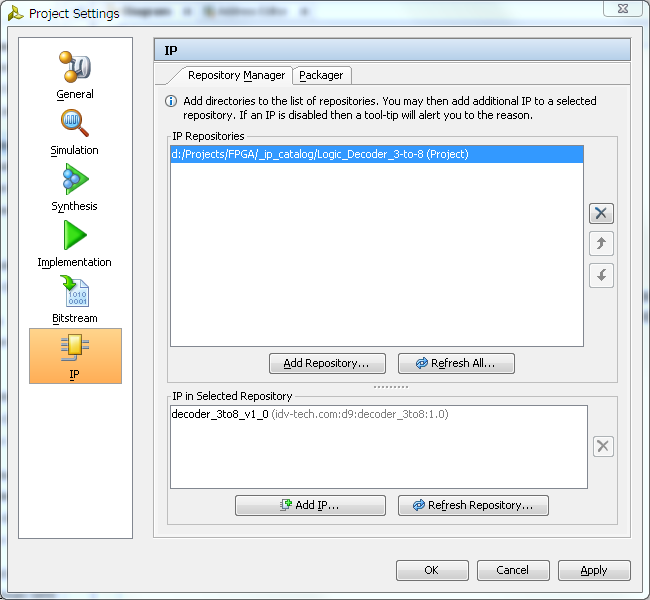

- Next we need to add our 3-to-8 decoder module to block diagram, but before we can do it, we must add it's repository to our project IP manager. So, in a 'Tools' menu select 'Project Settings' and then click on 'IP' icon.

- In 'IP' management dialog click on 'Add Repository...' button and specify our decoder IP project folder. Vivado will scan it, should find decoder IP and add it in found IP list. Click 'Apply' and then 'Ok' to close dialog.

- We can add decoder IP to our block diagram. Click on 'Add IP', typo decoder IP name and add it.

- Now we have to connect 3 SPI SS outputs to our decoder input, but we can't. Problem is that decoder inputs treated as a 'bus' and SPI SS outputs as individual 'wires'. One of the possible solution is to concatenate individual wires. In order to do it add Xilinx 'Concat' IP and modify it, so it will have 3 inputs.

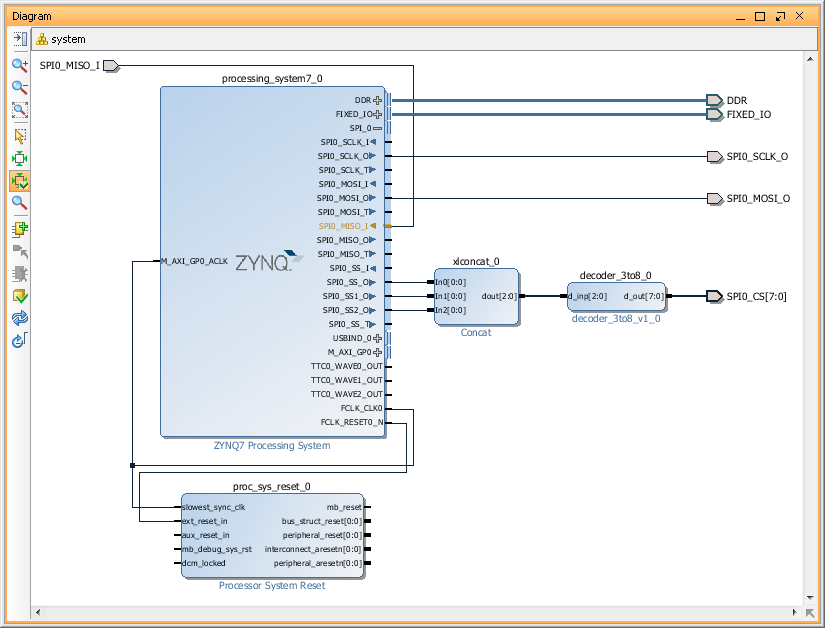

- Now we should be able to connect all blocks together. Specifically, connect SPI0_SS0, SPI0_SS1 and SPI0_SS2 to 'Concat' block input 0,1 and 2. Them, connect 'Concat' output to our 3-to-8 decoder IP and finally make decoder outputs 'External'. I will also rename output port to 'SPI0_CS'.

- This is basically it. Now we have to create 'constraints' file and specify in it Zynq PACKAGE_PIN for some or all pins of the 'SPI_CS0' port. For example you may want to export only 4 CS pins. Something like this:

- Later, in a software project, you will need to enable special option for SPI driver to use 'Slave Select' pins as encoded address. But that is part of another tutorial, but this one finished. Good luck!

module decoder_3to8(

input [2:0] d_inp,

output [7:0] d_out

);

assign d_out = (d_inp == 3'b000) ? 8'b00000001 :

(d_inp == 3'b001) ? 8'b00000010 :

(d_inp == 3'b010) ? 8'b00000100 :

(d_inp == 3'b011) ? 8'b00001000 :

(d_inp == 3'b100) ? 8'b00010000 :

(d_inp == 3'b101) ? 8'b00100000 :

(d_inp == 3'b110) ? 8'b01000000 :

8'b10000000;

endmodule

set_property IOSTANDARD LVCMOS33 [get_ports SPI0_SCLK] set_property IOSTANDARD LVCMOS33 [get_ports SPI0_MISO] set_property IOSTANDARD LVCMOS33 [get_ports SPI0_MOSI] set_property IOSTANDARD LVCMOS33 [get_ports SPI0_CS[0]] set_property IOSTANDARD LVCMOS33 [get_ports SPI0_CS[1]] set_property IOSTANDARD LVCMOS33 [get_ports SPI0_CS[2]] set_property IOSTANDARD LVCMOS33 [get_ports SPI0_CS[3]] set_property PACKAGE_PIN AA9 [get_ports SPI0_SCLK] set_property PACKAGE_PIN Y10 [get_ports SPI0_MISO] set_property PACKAGE_PIN AA11 [get_ports SPI0_MOSI] set_property PACKAGE_PIN W12 [get_ports SPI0_CS[0]] set_property PACKAGE_PIN W11 [get_ports SPI0_CS[1]] set_property PACKAGE_PIN V10 [get_ports SPI0_CS[2]] set_property PACKAGE_PIN W8 [get_ports SPI0_CS[3]]

This tutorial has so many error that i can't list all of them...